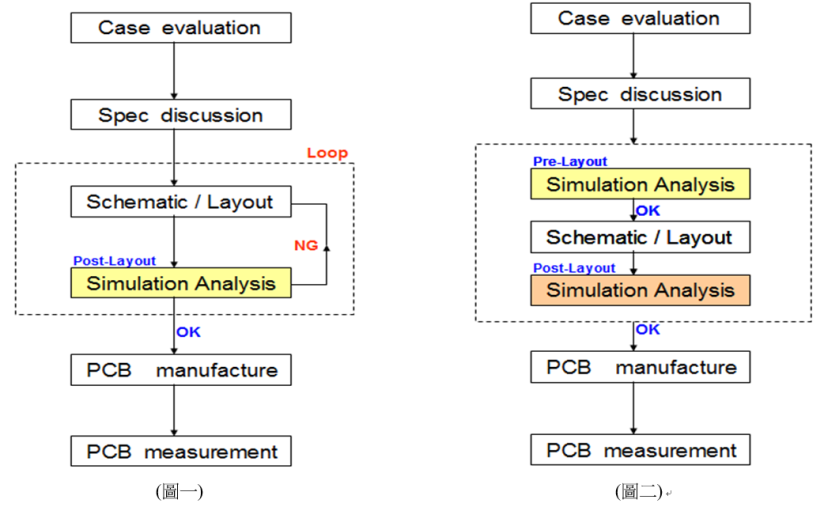

早期大家對SI ( Signal Integrity ) 的分析流程為:

設計人員設計完產品後再做分析,目的是希望可以減少因為設計不良所造成的成本問題,但是這對設計人員來說卻是件痛苦的事,因為所有的設計在此時都已經完成,但卻因為分析不過,又必須重頭來,修改結構或設計之類的事…而有時會因為尋找解決之道,反而影響了專案的時效性,因此,後期就有人把SI分析放在產品設計前,並於產品設計完後,做所謂的Post Simulation,更進一步確認訊號完整性的動作。但到了近期,有人甚至把SI分析拉到更前端,做所謂的Pre Simulation,因為SI的問題隨著產品時鐘頻率的上升,而顯得更難預測,因此,SI的Pre Simulation就變成了有什麼樣想法與如何找到適當的設計,所做的解決分法分析。

下兩張圖分別為早期產品設計與分析流程(圖一):因設計及分析不良,造成產品製作的無限迴圈,影響產品時效。與到後來修改為產品製作前與後的設計分析流程(圖二):大幅的提升設計成本與達到產品及早上市之可能。

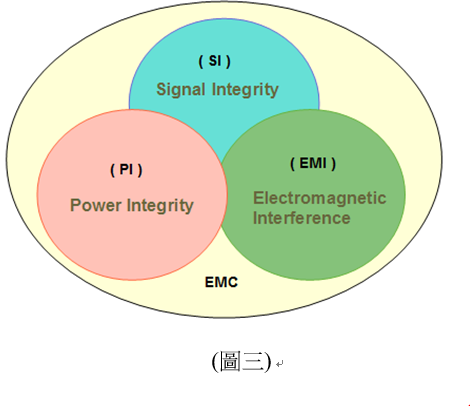

而另外要注意的是,SI與PI兩者是息息相關的,千萬別只顧一方。例如: SSN ( Simultaneous Switching Noise ) 就是PI造成SI的問題之一,而Boar Level 的 SI / PI 也會引發所謂的EMI/EMC等問題,而這些都是值得我們注意的地方。下圖(圖三)即為 SI/PI/EMI/EMC之間的關係圖。

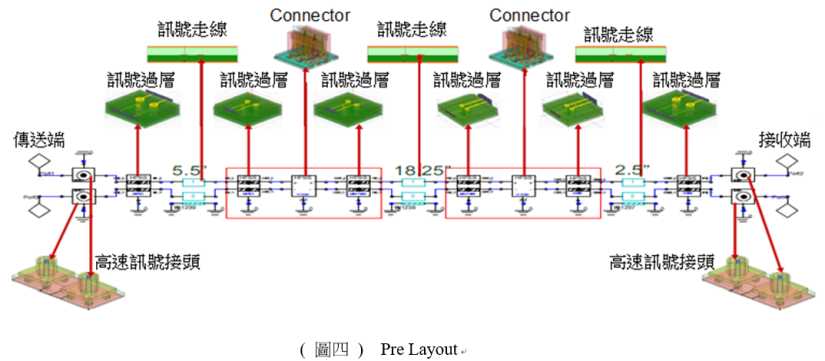

再來要談的就是如何做所謂的Pre Layout ( 即Pre Simulation )與Post Layout (即Post Simulation )。一般來說,訊號分成了兩種,Single Signal 與 Differential Signal ,而常見的高速訊號( 如: USB/DDR/SATA/HDMI/LVDS/PCI…等等 ),其所使用的方式均使用差動訊號對(Differential Pair) 來做呈現,而主要的目的是抗干擾( common model noise ),讓高速訊號能從傳送端順利的抵達到接收端。通常訊號在走線時,從一開始的訊號傳送到經過Component 再經由Trace至灌穿孔,作訊號換層的動作,最後再回到訊號接收端,這之間經過了許多互連(Interconnect)效應,並造成了許多的訊號反射(Multi-reflection) ,而降低了訊號的完整性,而透過全波電磁場軟體的模擬與運算,找出彼此之間的最佳化設計與做好阻抗匹配( Impedance Match),進而達到所需求的訊號品質,這即為初步的SI設計方法。另外,電源層設計的優化,也足夠優化了訊號的完整性,而這部分SI與PI的同步設計與模擬分析,將於後面的階段再做討論了! 以下先舉例高速訊號SI的硬體設計與模擬方式。

下圖(圖四)為一高速訊號通道,將所有訊號會經過的走線層,訊號過層(即灌穿孔及Connector、SMA接頭),把它們做模組化( Modeling )的分析。而這部份分成了2D Model走線層與3D Model ( VIA、Connector、Component…等等)兩部分,2D Trace 的部份較為好控制阻抗匹配,這當中的設計包括了,選用的走線方式與使用的材質、線寬、線長、層疊控制的設計等等…,而至於3D Model的部分就需要花心思設計了,因為這部分比較容易出現阻抗不連續,有所謂的寄生電容與電感效應,會造成許多的訊號反射,而過大的電容效應,其對訊號完整性來說是不好的,或過大的電感效應,則對電源完整性來說也是不好的。故將此所有的Model 作最佳化的分析,以達阻抗匹配為原則與目標來設計,而這階段的設計即為Pre Layout 設計手法的其中一環。

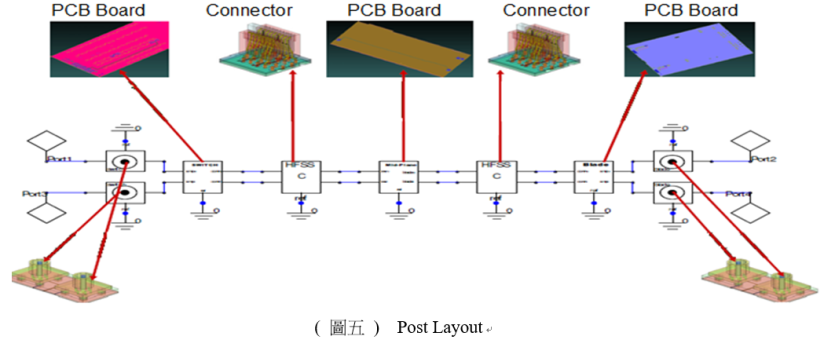

至於Post Layout的部分( 圖五 ),即為所有設計均完成後的分析,將所有的通道利用軟體萃取成仿RLGC的參數,並做SI 分析,確認與了解此通道在設計前與設計後分析的差異性,而在這個階段所遇到的SI問題也盡不同,此時SI問題有可能會出現也有可能不受影響,而會出現SI的問題有很多,諸如,有可能因為佈線時,線與線之間的耦合所造成的串音雜訊(Cross Talk Noise ),或是受其它因素的影響等等….而這些都是屬於產品設計完成後,所需做的確認動作,好讓工程師更了解此時訊號的好壞程度到哪,並做適時與適當的修正。

當然,各家解決SI/PI的手法與能力不盡相同,但共同的目的有三個:1. 時效( Timing ) 2. 成本( Cost ) 3. 效果(Performance),而解決訊號完整性的問題有許多,有些是不可預測的,以上例子只是SI解決的手法之一,但共同的想法為,如何透過模擬與分析,建立設計手法,並即早改善訊號的品質,這將是未來大家所關心的議題之一,最後,我們再來討論SI/PI Simulation 的應用。

其訊號完整性的分析是很廣的,從IC到Package再到PCB與機構甚至到全系統模擬,均可做垂直性整合分析。如(圖六),從一開始測試機台的訊號輸入端,經過Connector,再進入PCB板,最後到了Socket與IC端,而IC內部又包含了Package、Bond wire…等等,訊號在經過這麼多的結構之下,會產生許多的不連續效應,所以一定會有許多的訊號反射,但對早期時脈頻率較低的產品而言,其上升時間與下降時間較長,這對訊號完整性來說是沒有差的。但相較於現在的高速系統而言,訊號的品質就更顯得重要許多,因為這時候,一條走線也都有可能產生電磁波輻射,變成為傳輸線效應( transmission line ),進而引發EMI的問題,而這些問題,在早期是不會發生的。另外一個重點為,如何將模擬分析的數據作為實際可以參考的依據,其訊號的量測也顯得非常重要,因為這樣你才能掌握訊號的真實性,而非落於模擬的虛幻世界裡。

而常見的分析有哪些呢? 其主要是觀察頻域與時域的結果! 頻域的部分主要是觀察訊號的頻寬,包含了S參數,S21( insertion loss ) / S22( return loss ) ,或是Z參數,用來觀察電源層的目標阻抗等等…,而為什麼有時需要去觀察頻域,是因為有時在觀察時域的時候,顯小的差距是看不出的,因此必須透過頻域來觀察訊號品質的好壞。而時域的部分,其主要是看Transient、Overshoot、Undershoot、Delay time、Skew、TDR、Eye Diagram……等等,用來觀查某一時間與某一頻率下訊號品質的好壞。而在作這些分析時,所有的資訊與條件必須充足,這樣做出來的分析才較真實,才能更直接的找出問題的所在。

讀完您的文章 獲益良多 請問有聯絡方式能情教您嗎

讚讚

Hi JAMES 謝謝您~ 可以聯絡我的方式 spilinkshare99@gmail.com

讚讚

好感動(剛如行的實習EE)

讚讚